With physical access, instructions and data are vulnerable to inspection and modification as they get loaded from external memory and storage. Physical attacks such as bus snooping, memory interposing, side channel analysis, and cold boot; which enable these vulnerabilities, have proliferated—to the point that hobbyists can now perform them using consumer-grade equipment. The authentication and encryption provided by HMG mitigates these physical attacks by ensuring that loaded instructions are authentic and that data remains confidential through its entire lifecycle.

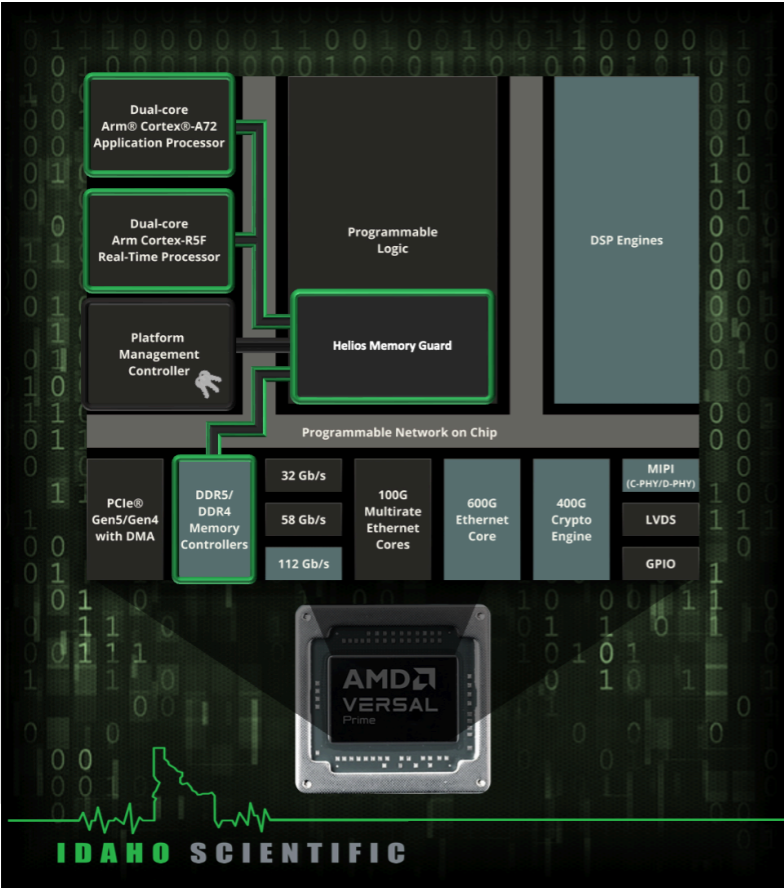

Helios Memory Guard (HMG) is shimmed in between the processor and memory controller to provide just-in-time encryption, decryption, and authentication for all memory write and read requests. This is done per cache line—in hardware—using ephemeral keys that roll on every write. HMG also performs decryption and authentication of boot/load-time images that have been encrypted by the Helios Packager prior to deployment. The user maintains full ownership and management of the load-time keys.

HMG has been verified for use with Xilinx ®7-Series, Ultrascale, Ultrascale+, and Versal. HMG can be ported for use with other FPGA vendor devices.

Yes, HMG has been taped out in 28nm as part of a RISC-V Helios Processing System. Additional ASIC projects are underway.

Idaho Scientific provides the Helios Packager utility, allowing the OEM or endcustomer to generate and manage their own cryptographic keys.

256-bit AES-GCM for both inline memory and data-at-rest load time encryption and verification. MLDSA-87 used for key management, with RSA-3072 provided for legacy support.

System designers can anticipate no memory throughput performance impacts until approaching bus saturation, at which point ~34% reduction is expected. More detailed performance data is available upon request.

HMG minimally utilizes ~60K LUTS and ~71k flip flops, and users can expect a ~250 MHz maximum frequency.